# Low Cost 5W Wireless Power Receiver

#### **Features**

- Single-Chip Solution up to 5-watt wireless power

- WPC/Qi v1.2 Standards Compatible

- Optimized for small coil designs

- ► Reliable low voltage startup

- ► Fixed 5.1V LDO regulated output

- ► High efficiency synchronous rectifier for system level efficiency up to 78%

- Output protection current limit

- ► Robust fully internal overvoltage protection

- Multifunction GPIO with switchable highprecision 20μA current source

- I<sup>2</sup>C Serial Interface, Enable input, Interrupt output

- -40°C to 85°C Operating Temperature Range

- Standard TQFN-24 package (5mm x 5mm x 0.750mm)

## **Brief Description**

KTE7200 is a robust single chip wireless power receiver optimized for low cost, low component count, and low cost PCB designs. This device is optimized for small low power devices with small coils, while also being capable of as much as 5 watts of output with an appropriate thermal design.

This is a microcontroller based design, optionally configurable by OTP memory, resistor programming features, and/or control via the I2C interface.

KTE7200 is highly integrated including 8k ROM, 8k OTP memory, an LDO regulator with OVP/OCP/RCP, and precision regulated DC output.

## **Applications**

- Earbud Cases, Mice, IoT Devices, Accessories

- Personal Care Products, Toys, etc.

- Other Battery-Powered Equipment

- Battery-free Devices using only wireless power

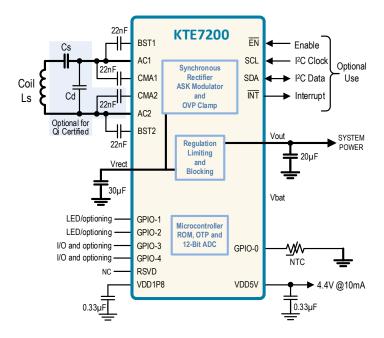

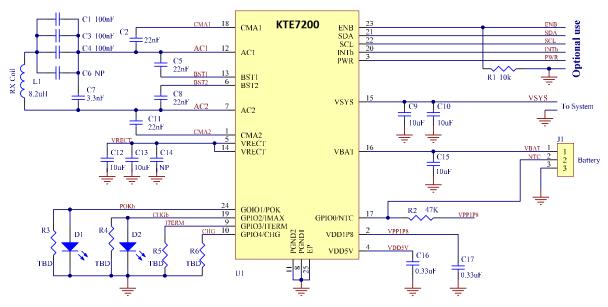

# **Typical Application**

# **Ordering Information**

| Part Number <sup>1</sup> | Marking <sup>2</sup>   | Default CV | Operating<br>Temperature | Package   |

|--------------------------|------------------------|------------|--------------------------|-----------|

| KTE7200EUAK-DA-TB        | KTE7200-DA<br>YYWWVXXX | 5.10V      | -40°C to +85°C           | TQFN55-24 |

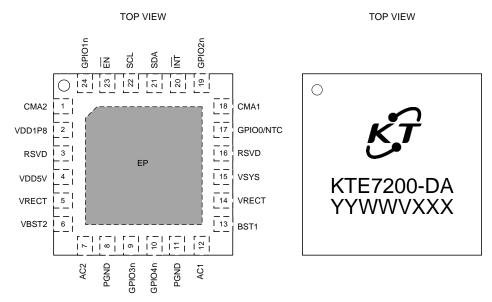

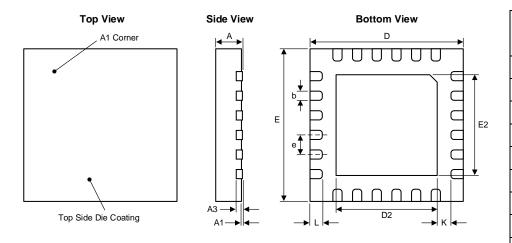

# **Pinout Diagram**

TQFN55-24

24-Pin 5mm x 5mm x 0.75mm TQFN Package, 0.65mm pitch

### **Top Mark**

DA = ROM Code

YY = Date Code (Year), WW = Date Code (Week), V = Assembly Code, XXX = Serial Number

<sup>1.</sup> Firmware code is included in the ordering part number. Please contact Kinetic Sales for further details.

<sup>2.</sup> DA = ROM Code, YY = Date Code (Year), WW = Date Code (Week), V = Assembly Code, XXX = Serial Number.

# **Pin Descriptions**

| Pin #  | Name      | Function                                                                                                                                       |

|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CMA2      | Wireless Power ASK Modulation – connect to modulation capacitor                                                                                |

| 2      | VDD1P8    | Internal 1.8V LDO Bias – connect an external $1\mu F$ bypass capacitor from this pin to the ground plane.                                      |

| 3      | RSVD      | Reserved. Leave floating (No connect).                                                                                                         |

| 4      | VDD5V     | Internal 5V LDO Bias – connect an external $1\mu F$ bypass capacitor from this pin to the ground plane.                                        |

| 5      | VRECT     | Rectified Output Voltage – connect to bulk storage capacitors                                                                                  |

| 6      | VBST2     | Boost Pin for AC2 – connect to AC2 bootstrap capacitor                                                                                         |

| 7      | AC2       | Rectifier Input #1 – connect to power delivery LC tank circuit                                                                                 |

| 8      | PGND      | Power Ground – connect directly to main ground plane                                                                                           |

| 9      | GPIO3     | General Purpose I/O – use as input/output per application                                                                                      |

| 10     | GPIO4     | GPIO-4 General Purpose I/O – use as input/output per application                                                                               |

| 11     | PGND      | Power Ground – connect directly to main ground plane                                                                                           |

| 12     | AC1       | Rectifier Input #1 – connect to power delivery LC tank circuit                                                                                 |

| 13     | VBST1     | Bootstrap Pin for AC1 – connect to AC2 bootstrap capacitor                                                                                     |

| 14     | VRECT     | Rectified Output Voltage – connect to bulk storage capacitors                                                                                  |

| 15     | VSYS      | Main System Voltage Output – connect to client system power bus                                                                                |

| 16     | RSVD      | Reserved – connect to ground.                                                                                                                  |

| 17     | GPIO0/NTC | GPIO-3 General Purpose I/O – connect to battery temperature thermistor or other input/output circuitry per application                         |

| 18     | CMA1      | Wireless Power ASK Modulation – connect to modulation capacitor                                                                                |

| 19     | GPIO2     | GPIO-1 General Purpose I/O – use as input/output per application                                                                               |

| 20     | ĪNT       | Active-Low Interrupt Open-Drain Output – optional output to client interrupt input function. Connect to ground if not used.                    |

| 21     | SDA       | I <sup>2</sup> C Data Input/Output – connect to the master's I <sup>2</sup> C data line and a pull-up resistor to the system I/O voltage rail. |

| 22     | SCL       | I <sup>2</sup> C Clock Input – connect to the master's I <sup>2</sup> C clock output and a pull-up resistor to the system I/O voltage rail.    |

| 23     | ĒN        | Active-Low Enable Input – connect to ground or logic 0 to enable the IC.                                                                       |

| 24     | GPIO1     | GPIO-1 General Purpose I/O – use as input/output per application.                                                                              |

| PADDLE | GND       | Ground paddle must be electrically connected to ground plane                                                                                   |

# **Absolute Maximum Ratings<sup>3</sup>**

| Symbol                               | Description                                      | Value                          | Units     |

|--------------------------------------|--------------------------------------------------|--------------------------------|-----------|

| $V_{RECT}$                           | VRECT to GND (without internal 25V clamp)        | -0.3 to 28                     | V         |

| $V_{\text{RECT}}$ - $V_{\text{SYS}}$ | VRECT to VSYS                                    | -6 to 28                       | V         |

| $V_{SYS}$                            | VSYS to GND                                      | -0.3 to 6                      | V         |

| $V_{SYS}$ - $V_{BAT}$                | VSYS to VBAT                                     | -6 to 6                        | V         |

| $V_{BAT}$                            | VBAT to GND                                      | -0.3 to 6                      | V         |

| $V_{DD5V}$                           | VDD5V to GND                                     | -0.3 to 6                      | V         |

| $V_{\text{DD1P8}}$                   | VDD1P8 to GND                                    | -0.3 to 2                      | V         |

| VEN                                  | EN to GND                                        | -0.3 to 6                      | V         |

| $V_{I2C}$                            | SCL, SDA, INT to GND                             | -0.3 to 6                      | V         |

| I <sub>VRECT-SYS</sub>               | VRECT to VSYS Continuous Current                 | 1.6                            | $A_{RMS}$ |

| $V_{AC}$                             | AC1, AC2 to PGND                                 | -0.3 to 26                     | V         |

| V <sub>RECT-AC</sub>                 | VRECT to AC1, VRECT to AC2                       | -0.3 to 26                     | V         |

| $V_{BST}$                            | BST1, BST2 to AGND                               | -0.3 to 26                     | V         |

| $V_{BST-AC}$                         | BST1 to AC1, BST2 to AC2                         | -0.3 to 6                      | V         |

| $V_{CM}$                             | CMA1, CMA2 to AGND                               | -0.3 to 26                     | V         |

| V <sub>EN</sub>                      | EN to AGND                                       | -0.3 to 28                     | V         |

| $V_{12C}$                            | SCL, SDA, INT to AGND                            | -0.3 to 6                      | V         |

| $V_{GPIO}$                           | GPIO0, GPIO1, GPIO2, GPIO3, GPIO4 to AGND        | -0.3 to V <sub>DD5V</sub> +0.3 | V         |

| lac                                  | AC1, AC2 Current                                 | 2.6                            | А         |

| Tı                                   | Operating Temperature Range                      | -40 to 140                     | °C        |

| Ts                                   | Storage Temperature Range                        | -55 to 150                     | °C        |

| T <sub>LEAD</sub>                    | Maximum Soldering Temperature (at leads, 10 sec) | 260                            | °C        |

# **ESD and Surge Ratings<sup>4</sup>**

| Symbol         | Description                                   | Value | Units |

|----------------|-----------------------------------------------|-------|-------|

| $V_{ESD\_HBM}$ | JEDEC JS-001-2017 Human Body Model (all pins) | ±2    | kV    |

<sup>3.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>4.</sup> ESD Ratings conform to JEDEC standards.

# **Thermal Capabilities**<sup>5</sup>

| Symbol              | Description                                                | Value  | Units |

|---------------------|------------------------------------------------------------|--------|-------|

| ΘJA                 | Thermal Resistance – Junction to Ambient                   | 30.16  | °C/W  |

| Θ <sub>ЈВ</sub>     | Thermal Resistance – Junction to Board                     | 8.06   | °C/W  |

| P <sub>D</sub>      | Maximum Power Dissipation at 25°C (T <sub>J</sub> = 125°C) | 3.32   | W     |

| ΔΡ <sub>D</sub> /ΔΤ | Derating Factor Above T <sub>A</sub> = 25°C                | -33.17 | mW/°C |

# **Recommended Operating Conditions**

| Symbol              | Description                         | Value      | Units |

|---------------------|-------------------------------------|------------|-------|

| V <sub>RECT</sub>   | Input operating voltage             | 3.6 to 10  | V     |

| Csys                | Sustain author canacitar            | 10         | μF    |

| CSYS                | System output capacitor             | 6.3        | V     |

|                     | TV higs LDO output conscitor        | 0.33       | μF    |

| C <sub>VDD5V</sub>  | 5V bias LDO output capacitor        | 6.3        | V     |

|                     | 1.9V bias LDO output canasitar      | 0.33       | μF    |

| C <sub>VDD1P8</sub> | 1.8V bias LDO output capacitor      | 6.3        | V     |

| TA                  | Ambient Operating Temperature Range | -40 to 85  | °C    |

| TJ                  | Die Operating Temperature Range     | -40 to 140 | °C    |

<sup>5. 4-</sup>layers PCB, air velocity = 0 m/s. Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

### **Electrical Characteristics**

Unless otherwise noted, the *Min* and *Max* specs are applied over the recommended operation temperature range of -40°C to +85°C and  $V_{RECT} = 3.6V$  to 10V. Typical values are specified at  $T_A = +25$ °C with  $V_{RECT} = 6V$ .

### **Supply Specifications (IN)**

| Symbol                          | Description                  | Conditions                      | Min | Тур | Max | Units |

|---------------------------------|------------------------------|---------------------------------|-----|-----|-----|-------|

| Thermal Shutdown Specifications |                              |                                 |     |     |     |       |

| т                               | IC Junction Thermal Shutdown | T <sub>J</sub> rising threshold |     | 140 |     | °C    |

| T <sub>J_SHDN</sub>             | ic junction mermai shutdown  | Hysteresis                      |     | 20  |     | °C    |

| Thermal Shutdown Specifications |                              |                                 |     |     |     |       |

| RON_CMA                         | CMA1, CMA2 On Resistance     | I <sub>CMA</sub> = 200mA        |     | 1   |     | W     |

| I <sub>CMA_LK</sub>             | CMA1, CMA2 Leakage Current   | V <sub>CMA</sub> = 10V          |     | 1   |     | μΑ    |

## Supply, Bias & Power Selector Specifications (VRECT, VBAT, VDD5V, VDD1P8)

| Symbol                | Description                                | Conditions                                                                                            | Min                  | Тур                  | Max                  | Units       |

|-----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------------|

| V <sub>RECT</sub>     | VRECT Operating Range <sup>6</sup>         |                                                                                                       | 3.6                  |                      | 10                   | V           |

| V <sub>UVP_RECT</sub> | VRECT Under-Voltage Lockout Protection     | Rising threshold<br>Hysteresis                                                                        | 2.9                  | 3.2<br>250           |                      | V<br>mV     |

| Ivrect                | VRECT No-Load Supply Current               | Enabled, $\overline{EN} = 0$ , $V_{RECT} = 6.0V$<br>Shutdown, $\overline{EN} = 1$ , $V_{RECT} = 6.0V$ |                      | 10<br>100            |                      | mA<br>μA    |

| V <sub>DD5V</sub>     | VDD5V Output Voltage register 0xE2 = 0x02  | $V_{RECT} = 3.6V^6$ $V_{RECT} = 6.0V^6$ $V_{RECT} = 10V$                                              | 4.28<br>4.28         | 3.55<br>4.38<br>4.38 | 4.48<br>4.48         | V<br>V<br>V |

| V <sub>DD1P8</sub>    | VDD1P8 Output Voltage register 0xE6 = 0x80 | $V_{RECT} = 3.6V^6$ $V_{RECT} = 6.0V^6$ $V_{RECT} = 10V$                                              | 1.70<br>1.70<br>1.70 | 1.75<br>1.75<br>1.75 | 1.80<br>1.80<br>1.80 | V<br>V<br>V |

| f <sub>clk</sub>      | Internal clock frequency                   |                                                                                                       | -2%                  | 4                    | +2%                  | Mhz         |

### Logic Pin Specifications (EN, INT, POK, CHG)

| Symbol            | Description                          | Conditions                | Min | Тур   | Max | Units |

|-------------------|--------------------------------------|---------------------------|-----|-------|-----|-------|

| V <sub>IH</sub>   | Input Logic High (EN)                |                           | 1.2 |       |     | V     |

| $V_{IL}$          | Input Logic Low (EN)                 |                           |     |       | 0.4 | V     |

| I <sub>I_LK</sub> | Input Logic Leakage (EN)             | $T_A = 25$ °C, $V_I = 5V$ | -1  | ±0.01 | 1   | μΑ    |

| V <sub>OL</sub>   | Output Logic Low (INT, POK, CHG)     | I <sub>O_SINK</sub> = 1mA |     |       | 0.4 | V     |

| lo_lk             | Output Logic Leakage (INT, POK, CHG) | TA = 25°C, VO = 5V        |     | 0.01  | 1   | μΑ    |

(continued next page)

<sup>6.</sup> These electrical parameters are Guaranteed by Characterization (GBC) and/or Guaranteed by Design (GBD).

## **Electrical Characteristics (continued)**

Unless otherwise noted, the *Min* and *Max* specs are applied over the recommended operation temperature range of -40°C to +85°C and  $V_{RECT} = 3.6V$  to 10V. Typical values are specified at  $T_A = +25$ °C with  $V_{RECT} = 6.0V$ .

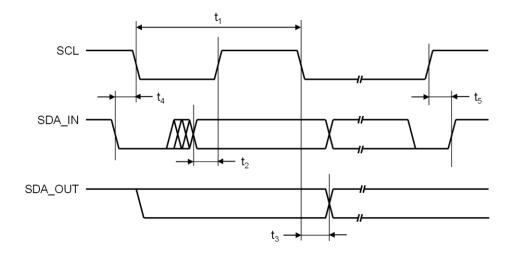

## I<sup>2</sup>C Compatible Interface Specifications (SCL, SDA)

| Symbol         | Description                                           | Conditions             | Min | Тур | Max | Units |

|----------------|-------------------------------------------------------|------------------------|-----|-----|-----|-------|

| $V_{RECT}$     | VRECT Operating Range <sup>6</sup>                    |                        | 3.6 |     | 10  | V     |

| VIL            | Input Logic Low Threshold                             |                        |     |     | 0.4 | V     |

| Vol            | SDA Output Logic Low                                  | I <sub>SDA</sub> = 3mA |     |     | 0.4 | V     |

| t <sub>1</sub> | SCL clock period <sup>6</sup>                         |                        | 2.5 |     |     | μs    |

| t <sub>2</sub> | Data in setup time to SCL high <sup>6</sup>           |                        | 100 |     |     | ns    |

| t <sub>3</sub> | Data out stable after SCL low <sup>6</sup>            |                        | 0   |     |     | ns    |

| t <sub>4</sub> | SDA low setup time to SCL low (Start) <sup>6</sup>    |                        | 100 |     |     | ns    |

| t <sub>5</sub> | SDA high hold time after SCL high (Stop) <sup>6</sup> |                        | 100 |     |     | ns    |

Figure 1. I<sup>2</sup>C Compatible Interface Timing Diagram

# **Electrical Characteristics (continued)**

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of -40°C to +85°C and  $V_{IN}$  = 2.5V to 5.5V. Typical values are specified at  $T_A$  = +25°C and  $V_{IN}$  = 5V.

## **OVP/LDO Specifications (VRECT to VSYS)**

| Symbol                | Description                                               | Conditions                                                                                                                                     | Min | Тур       | Max | Units       |

|-----------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-----|-------------|

| V <sub>RECT</sub>     | VRECT Operating Range                                     |                                                                                                                                                | 3.6 |           | 10  | V           |

| V <sub>OVP_RECT</sub> | VRECT Over-Voltage Protection                             | Rising threshold                                                                                                                               |     |           | 28  | V           |

| I <sub>OCP_LDO</sub>  | Over-Current Protection                                   |                                                                                                                                                |     | 3         |     | Α           |

| Ron_ldo               | OVP/LDO On-Resistance                                     | VRECT to VSYS                                                                                                                                  |     | 0.5       |     | Ω           |

| I <sub>LK_LDO</sub>   | Off Leakage Current                                       | V <sub>RECT</sub> = 20V, V <sub>SYS</sub> = 0V, T <sub>A</sub> = 25°C<br>V <sub>RECT</sub> = 20V, V <sub>SYS</sub> = 5V, T <sub>A</sub> = 25°C |     | 1<br>5    |     | μA<br>μA    |

| C <sub>VLDO</sub>     | VRECT-to-VSYS Constant Voltage<br>Regulation <sup>6</sup> | Setting range in 20mV steps<br>Accuracy at T <sub>A</sub> = 25°C<br>Default Setting for KTE7200                                                | 3.2 | ±5<br>5.1 | 5.2 | V<br>%<br>V |

| V <sub>SYS_LDR</sub>  | VSYS Load Regulation                                      | LDO Mode                                                                                                                                       |     | 150       |     | mV/A        |

| V <sub>SYS_LNR</sub>  | VSYS Line Regulation                                      | LDO Mode                                                                                                                                       |     | 5         |     | mV/V        |

| I <sub>SYS_PEAK</sub> | Peak Current Capability <sup>6</sup>                      |                                                                                                                                                |     | 1.5       |     | Α           |

| V <sub>RECT-SYS</sub> | VRECT to VSYS Dropout Voltage                             | I <sub>SYS</sub> = 10mA; V <sub>RECT</sub> droops 10%<br>below the LDO regulated output<br>value                                               |     | 100       |     | mV          |

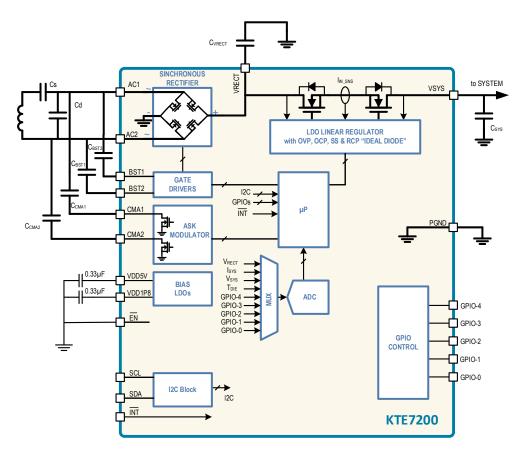

## **Functional Block Diagram**

Figure 2. Functional Block Diagram

## **Functional Description**

The KTE7200 integrates a 5W wireless power receiver that conforms to WPC/Qi v1.2 Baseline Power Profile (BPP) standards. AC power is coupled through the connected coil via magnetic induction.

#### **Full-Bridge Synchronous Rectifier**

The KTE7200 includes a full-bridge synchronous rectifier comprised of four low-RDSON MOSFET switches for high-efficiency AC-to-DC power conversion. The AC input to the rectifier is at pins AC1 and AC2, while the DC output is from pins VRECT to PGND. The rectified DC voltage and energy are stored on the off-chip capacitors connected to the VRECT pin. The rectifier's inputs, MOSFETs, and output are rated to 26V absolute maximum for robust and reliable performance.

#### **Proprietary Overvoltage Protection**

Proprietary overvoltage protection precisely limits the rectifier output to protect the KTE7200 during transient events, such as when dynamically moving the receiver coil on the transmitter pad. Conventional solutions rely upon external bulk capacitors or ISINK resistors to dissipate extra energy and prevent excessive voltage. Instead, the KTE7200 utilizes a proprietary solution that is more robust, does not require any external components, and precisely limits VRECT to 25V.

#### **Low-dropout Linear Regulator**

The KTE7200 integrates a high-power, low-dropout (LDO) linear regulator that provides a stable and accurate DC output for system loads up to 0.7A while output voltage is 5.1V. The LDO includes important features such as over-voltage protection (OVP), and over-current protection (OCP).

- Output Short-Circuit Protection (SCP) The high-power LDO is rated to support up to 1A loads. For output over-load and short-circuit conditions, the LDO includes short-circuit protection.

- Output Under-Voltage Protection (UVP) The KTE7200 includes under-voltage protection when VOUT falls below 3.0V.

- Output Over-Voltage Protection (OVP) The KTE7200 includes output over-voltage protection that enables a 10mA current sink at VSYS whenever the output voltage exceeds its nominal regulation set-point by more than 15%. The current sink is disabled when the output voltage returns to within 10% above nominal. This reduces VSYS voltage soar during dynamic load conditions or when the transmitter-to-receiver distance is physically modulated.

The LDO's input is internally connected to the rectifier's output at VRECT, while the regulated output is at VSYS. Communications from the KTE7200 back to the WPC transmitter automatically adjust the transmitter's output power such that the VRECT maintains sufficient headroom for the LDO.

#### **Die Temperature Monitor**

The die temperature implements fail-safe thermal shutdown during fault or excessive heat conditions.

#### **Analog-to-Digital Converter (ADC)**

Analog-to-Digital Converter (ADC) – The ADC has an input multiplexor (MUX) to sense various voltages, currents, and temperatures.

#### **Embedded Microcontroller and OTP Memory**

The KTE7200 includes an embedded microcontroller with 8K bytes of one-time programmable (OTP) memory and firmware.

### **Optional** EN Input

The KTE7200 has an optional  $\overline{\text{EN}}$  logic input pin to enable and disable the IC. Because the KTE7200 is powered from its wireless input, simply connect the  $\overline{\text{EN}}$  pin to ground for automatic enable/disable operation whenever the receiver is placed on a transmitter or removed, respectively. In applications that require to disable the wireless charger portion for various reasons while the receiver is on the transmitter, optionally drive the  $\overline{\text{EN}}$  pin with logic 1 for shutdown mode.

### Optional EN Flag

The KTE7200 includes an optional I<sup>2</sup>C serial interface and open-drain interrupt flag intended for use in customized and future versions of the KTE7200. Consult an authorized Kinetic Technologies representative for more information.

#### **GPIO Pins and Optional Configuration**

The KTE7200 has five GPIO pins, GPIO0 through GPIO4, which may be used for optional configuration.

Each GPIO is configurable to support a precision internal 20µA current source. Depending upon the application, GPIOs may be left floating (no connect), shorted to ground, or connected to an external setting resistor.

#### **Standard Firmware**

The standard firmware in the KTE7200 aligns with the WPC/Qi v1.2 Baseline Power Profile (BPP) standards and can operate autonomously without intervention from the system's applications processor.

#### **Custom Firmware Development**

For high-volume applications, Kinetic Technologies may develop customized firmware to meet specialized customer needs. Consult an authorized Kinetic Technologies representative for more information.

## **Application Schematic**

Figure 3. Application Schematic

#### **Bill of Materials**

| Item | Quantity | Reference       | Description                                          | Value   | Manufacturer         |

|------|----------|-----------------|------------------------------------------------------|---------|----------------------|

| 1    | 4        | C1, C3, C4, C6  | CAP CER 0.1µF 50V X5R                                | 100nF   | Murata               |

| 2    | 2        | C2, C5, C8, C11 | CAP CER 0.022µF 50V X7R                              | 22nF    | Yageo                |

| 3    | 1        | C7              | CAP CER 3300PF 50V X7R                               | 3.3nF   | Yageo                |

| 5    | 3        | C12, C13, C14   | CAP CER 10μF 25V X5R                                 | 10μF    | Murata               |

| 5    | 2        | C9, C10, C15    | CAP CER 10μF 16V X5R                                 | 10μF    | Murata               |

| 6    | 2        | C16, C17        | CAP CER 1µF 10V X5R                                  | 1μF     | Yageo                |

| 7    | 2        | D1, D2          | LED GREEN CLEAR 0603 SMD                             | Green   | Any                  |

| 8    | 1        | R47             | RES 47KΩ 1% 1/4W 0402                                | 47K     | Any                  |

| 9    | 1        | R1              | RES 10KΩ 1% 1/4W 0402                                | 10K     | Any                  |

| 10   | 4        | R3, R4, R5, R6  |                                                      | TBD     | Any                  |

| 11   | 1        | U1              | Wireless power receiver/charger                      | KTE7200 | Kinetic Technologies |

| 12   | 1        | RX coil         | WPC receive coil, L = $8.2\mu$ H, ACR = $0.22\Omega$ | 8       | 1                    |

#### **External Component Selection**

#### **Coil Selection**

Select a coil that meets the needs of the application. Consider form-factor, series resistance and inductance. Larger diameter coils generally perform better. Use a shield that is sufficient to prevent magnetic flux from interacting with metallic objects elsewhere in the application. To obtain WPC/Qi certification, the receiver must work with all WPC/Qi certified transmitters.

#### **Capacitor Selection**

Ceramic capacitors with X5R, X6S, or X7R ratings are recommended due to their low ESR, low ESL, low temperature coefficients, and small physical sizes. Consider the voltage rating, size, and DC bias derating characteristic of the capacitor.

#### Cs and Cd Capacitor Selection

Choose Cs and Cd per the guidelines set forth by the WPC/Qi specifications. Use small ceramic capacitors with 50V or more rating.

Select the value of Cs for primary resonance at 100kHz:

$$f_S = \frac{1}{2\pi\sqrt{L'_S C_S}} = 100kHz$$

where L'S is the self-inductance of the coil when placed and aligned on the interface surface of a power transmitter.

Select the value of Cd for secondary resonance at 1MHz:

$$f_d = \frac{1}{2\pi \sqrt{L_s \left(\frac{1}{C_s} + \frac{1}{C_d}\right)^{-1}}} = 1MHz$$

where L<sub>S</sub> is the self-inductance of the coil when away from the interface surface of a power transmitter but including any "friendly" magnetic material that is part of the receiver design.

#### C<sub>BSTn</sub> Capacitor Selection

Choose ceramic boost capacitors with voltage rating of 50V and 22nF nominal capacitance. Typically, 0402 (1005M) case-size is sufficient.

#### C<sub>CMAn</sub> Capacitor Selection

Choose ceramic modulation capacitors with voltage rating of 50V and 22nF nominal capacitance. Typically, 0402 (1005M) case-size is sufficient.

#### **CRECT Capacitor Selection**

Choose ceramic rectifier output capacitor(s) with voltage rating of 25V or more, and  $4.7\mu F$  to  $22\mu F$  total nominal capacitance. Typically, two  $10\mu F$  capacitors in parallel, each with 0603 (1608M) case-size or larger, is a good choice. Larger values and larger case-size provide more effective capacitance when considering the DC bias derating characteristic of the capacitor.

#### **CSYST Capacitor Selection**

Choose ceramic VSYS output capacitor(s) with voltage rating of 6.3V or more and  $10\mu F$  total nominal capacitance or more. Larger values and larger case-size provide more effective capacitance when considering the DC bias derating characteristic of the capacitor.

#### CVDD5V and CVDD1P8 Capacitor Selection

Choose ceramic VDD5V and VDD1P8 output capacitors with voltage rating of 6.3V or more and  $1\mu$ F nominal capacitance each. Typically, 0402 (1005M) case-size is sufficient.

# **Packaging Information**

TQFN55-24 (5.00mm x 5.00mm x 0.75mm)

| Dimension | mm        |      |      |

|-----------|-----------|------|------|

|           | Min.      | Тур. | Max. |

| Α         | 0.70      | 0.75 | 0.80 |

| A1        | 0.00      | 0.02 | 0.05 |

| A3        | 0.203 REF |      |      |

| b         | 0.25      | 0.30 | 0.35 |

| D         | 5.00 BSC  |      |      |

| D2        | 3.25      | 3.30 | 3.35 |

| E         | 5.00 BSC  |      |      |

| E2        | 3.25      | 3.30 | 3.35 |

| е         | 0.65 BSC  |      |      |

| K         | 0.20      |      | _    |

| L         | 0.35      | 0.40 | 0.45 |

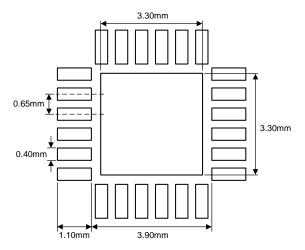

### **Recommended Footprint**

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.