# 4.5 Amp Overvoltage Protection IC with Surge Protection

### **Features**

- Wide Input voltage range: 2.3V to 28V

- Up to 4.5A Continuous current capability

- Integrated 36mΩ (typ) N-Channel MOSFET

- Wide Overvoltage threshold range

- Fixed internal: 6.4VAdjustable: 4V to 24V

- Fast OVP response time: 0.1µs (typ.)

- Internal 15ms Startup Debounce

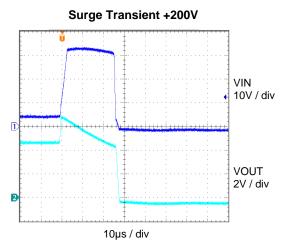

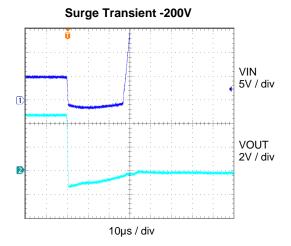

- Integrated Surge Protection up to +/-200V

- Low Quiescent Current: 100µA (typ.)

- Thermal Shutdown and Short Circuit Protection

- Compliance to IEC61000-4-2 (Level 4)

- ▶ Contact: ±8kV▶ Air Gap: ±15kV

- ESD Protection

- ► Human Body Model: ±2kV

- Pb-free Package: 12-Bump WLCSP

- -40°C to +85°C Temperature Range

### **Brief Description**

The KTS1650B overvoltage protection (OVP) device features an ultra-low  $36m\Omega$  (typical) on-resistance high current integrated MOSFET which actively protects low-voltage systems from voltage supply faults up to  $+28V_{DC}$ . An internal clamp protects the device from surges up to 200V.

An input voltage exceeding the overvoltage threshold will cause the internal MOSFET to turn off, preventing excessive voltage from damaging downstream devices. When the OVLO input set below the external OVLO select voltage, the KTS1650B automatically chooses the internal fixed OVLO threshold, preset to 6.4V (typical). The overvoltage protection threshold can be adjusted with optional resistor divider to a voltage between 4V and 24V.

The KTS1650B is protected against over-current faults by an internal over-temperature protection shutdown feature.

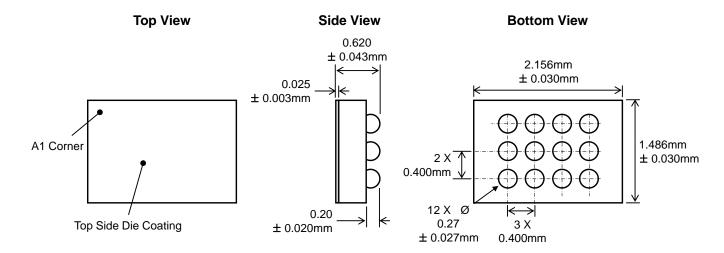

The KTS1650B is available in a RoHS and Green compliant 12-Bump 2.156mm x 1.486mm x 0.620mm WLCSP.

## **Applications**

- Smartphones

- Tablet

- Mobile Internet Devices, Peripherals

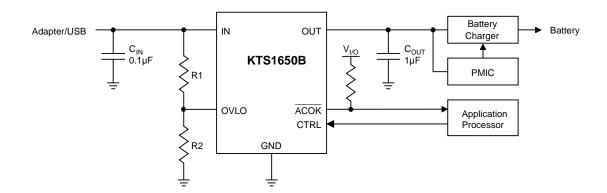

## **Typical Application**

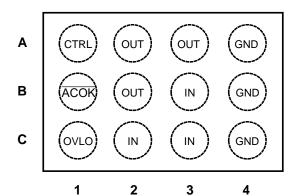

## **Pin Descriptions**

| Pin #                                                                                                                                                              | Name | Function                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 CTRL OUT power path is Enabled when CTRL is logic Low.  A2, A3, B2 OUT Output of internal main high-current power switch. Connect OUT pins to proper operation. |      | OUT power path is Enabled when CTRL is logic Low.                                                                                                                                                                                              |

|                                                                                                                                                                    |      | Output of internal main high-current power switch. Connect OUT pins together in the PCB for proper operation.                                                                                                                                  |

| A4, B4, C4                                                                                                                                                         | GND  | Ground. Connect GND pins together in the PCB for proper operation.                                                                                                                                                                             |

| B1 ACOK impeda                                                                                                                                                     |      | Open-drain power good output. ACOK is driven low during normal operation and becomes high impedance when an out-of-range condition is detected. Connect a pull-up resistor between the logic pin and the system rail.                          |

| B2, C2, C3 IN Voltage Input. Connect IN pins together in the PCB for proper operation.                                                                             |      | Voltage Input. Connect IN pins together in the PCB for proper operation.                                                                                                                                                                       |

| C1                                                                                                                                                                 | OVLO | External OVLO Adjustment. Connect OVLO to GND when using the internal fixed threshold. Connect a resistor-divider to OVLO to set the adjustable OVLO threshold. The optional external resistor divider is unrelated to the internal threshold. |

### WLCSP-12

TOP VIEW TOP VIEW

12-Bump 2.156mm x 1.486mm x 0.620mm WLCSP Package

### **Top Mark**

WW = Device ID Code

XX = Date Code, YY = Assembly Code

ZZZZ = Serial Number

# Absolute Maximum Ratings<sup>1</sup>

#### $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol          | ·                                                |                                 | Units |

|-----------------|--------------------------------------------------|---------------------------------|-------|

| IN <sup>2</sup> | IN to GND and IN to OUT = GND or Float           | -2 <sup>3</sup> to 29           | V     |

| OUT             | OUT to GND                                       | -0.3 to<br>V <sub>IN</sub> +0.3 | V     |

| OVLO            | OVLO Pin                                         | -0.3 to 7                       | V     |

| CTRL, ACOK      | Control Pin and ACOK Pin                         | -0.3 to 6                       | V     |

| IN OUT Current  | Continuous Current                               | 4.5                             | А     |

| IN, OUT Current | Peak Current (10msec)                            | 8.0                             | Α     |

| TJ              | Operating Temperature Range                      | -40 to 150                      | °C    |

| Ts              | Storage Temperature Range                        | -65 to 150                      | °C    |

| TLEAD           | Maximum Soldering Temperature (at leads, 10 sec) | 260                             | °C    |

## **Thermal Capabilities**

| Symbol                | Description                                                           | Value | Units |

|-----------------------|-----------------------------------------------------------------------|-------|-------|

| θја                   | θ <sub>JA</sub> Thermal Resistance – Junction to Ambient <sup>4</sup> |       | °C/W  |

| PD                    | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C                    | 1.6   | W     |

| $\Delta P_D/\Delta T$ | Derating Factor Above T <sub>A</sub> = 25°C                           | -12.6 | mW/°C |

# ESD and Surge Ratings<sup>5</sup>

| Symbol                | Description                             | Value | Units |

|-----------------------|-----------------------------------------|-------|-------|

| V <sub>ESD_</sub> HBM | JESD22-A114 Human Body Model (all pins) | ±2    | kV    |

| V <sub>ESD_CD</sub>   | IEC61000-4-2 Contact Discharge (VBUS)   | ±8    | kV    |

| Vesd_agd              | IEC61000-4-2 Air Gap Discharge (VBUS)   | ±15   | kV    |

| Vsurge                | IEC61000-4-5 Surge (VBUS to GND)        | ±200  | V     |

# **Ordering Information**

| Part Number    | Marking <sup>6</sup> | OVLO<br>Threshold | Operating Temperature | Package  |

|----------------|----------------------|-------------------|-----------------------|----------|

| KTS1650BEVG-TR | MSXXYYZZZZ           | 6.4V              | -40°C to +85°C        | WLCSP-12 |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Survives burst pulse up to 200V with  $2\Omega$  series resistance.

<sup>3.</sup> Pulsed, 50ms maximum non-repetitive.

<sup>4.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board. Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board.

ESD and Surge Ratings conform to JEDEC and IEC industry standards. Some pins may actually have higher performance. Surge ratings apply with chip enabled, disabled, or unpowered, unless otherwise noted.

<sup>6.</sup> WW = Device ID Code, XX = Date Code, YY = Assembly Code, ZZZZ = Serial Number.

# **Electrical Characteristics**<sup>7</sup>

$V_{IN}$  = +2.3V to +28V and  $C_{IN}$  = 1.0nF. Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of -40°C to +85°C, while *Typ* values are specified at room temperature (25°C).  $V_{IN}$  = 5V,  $I_{IN}$   $\leq$  4.5A.

| Symbol                | Description                             | Conditions                                                                                                 | Min  | Тур  | Max | Units |

|-----------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| Charging              | Mode (VCTRL = 0V)                       |                                                                                                            | •    | •    | •   |       |

| Vin                   | Input Voltage Range                     |                                                                                                            | 2.3  |      | 28  | V     |

| V <sub>IN_CLAMP</sub> | Input Clamp Voltage                     | I <sub>IN</sub> = 10mA, T <sub>A</sub> = +25°C                                                             |      | 32   |     | V     |

| I <sub>IN</sub>       | Input Supply Current                    | VIN = 5V, VIN < VOVLO                                                                                      |      | 100  | 200 | μА    |

| $V_{\text{IN\_UVLO}}$ | Under voltage lockout threshold         | V <sub>IN</sub> rising                                                                                     |      | 1.9  |     | V     |

| Vuvlo_HYS             | Under voltage lockout hysteresis        |                                                                                                            |      | 0.1  |     | V     |

| OVP                   |                                         |                                                                                                            |      |      |     |       |

| V <sub>IN_OVLO</sub>  | Internal Overvoltage Trip Level         | V <sub>IN</sub> rising, T <sub>A</sub> = +25°C                                                             |      | 6.4  |     | V     |

| VIN_OVLO_HY           | S OVLO Hysteresis                       | V <sub>IN</sub> falling, T <sub>A</sub> = 25°C                                                             |      | 0.3  |     | V     |

| $V_{\text{OVLO\_TH}}$ | OVLO Set Threshold                      | V <sub>IN</sub> rising, T <sub>A</sub> = +25°C                                                             |      | 1.22 |     | V     |

| V <sub>OVLO_EXT</sub> | Adjustable OVLO Select Threshold        |                                                                                                            | 4    |      | 24  | V     |

| Vovlo_sel             | External OVLO Set Threshold range       |                                                                                                            | 0.2  | 0.25 | 0.3 | V     |

| Ron                   | OVLO Switch On-Resistance               | V <sub>IN</sub> = 5V, T <sub>A</sub> = +25°C                                                               |      | 36   |     | mΩ    |

| IOUT_LEAK             | OUT Leakage Current                     | VIN = VIN_OVLO, VOUT = 5V                                                                                  |      | 8    | 12  | μΑ    |

| l <sub>ovlo</sub>     | OVLO Input Leakage Current              | V <sub>OVLO</sub> = V <sub>OVLO_TH</sub>                                                                   | -100 |      | 100 | nA    |

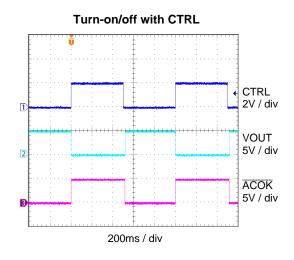

| CTRL                  |                                         |                                                                                                            |      |      |     |       |

| V <sub>CTRL_H</sub>   | CTRL logic high threshold               |                                                                                                            | 1.4  |      |     | V     |

| Vctrl_l               | CTRL logic low threshold                |                                                                                                            |      |      | 0.4 | V     |

| <b>Digital Sig</b>    | nals (ACOK)                             |                                                                                                            |      |      |     |       |

| $V_{OL}$              | ACOK output low voltage                 | $V_{I/O} = 3.3V$ , $I_{SINK} = 1mA$                                                                        |      |      | 0.4 | V     |

| VACOK_LEAR            | ACOK leakage current                    | $V_{I/O} = 3.3V$ , $\overline{ACOK}$ de-asserted                                                           | -1   |      | 1   | μΑ    |

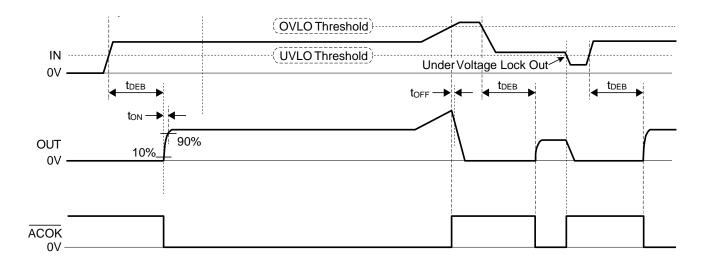

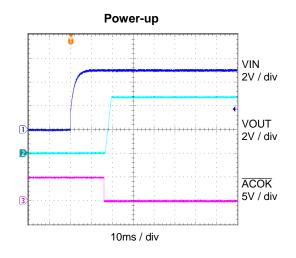

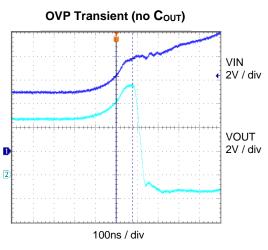

| Timing Ch             | aracteristics (Figure-1)                |                                                                                                            |      |      |     |       |

| t <sub>DEB</sub>      | Debounce Time                           | Time from 2.1V $<$ V <sub>IN</sub> $<$ V <sub>IN_OVLO</sub> to V <sub>OUT</sub> $=$ 10% of V <sub>IN</sub> |      | 15   |     | ms    |

| t <sub>ON</sub>       | Ramp Time                               | V <sub>OUT</sub> = 10% of V <sub>IN</sub> to 90% of V <sub>IN</sub>                                        |      | 2    |     | ms    |

| toff_res              | Switch Turn-Off Response Time           | V <sub>IN</sub> > V <sub>OVLO</sub> to V <sub>OUT</sub> stop rising                                        |      | 100  |     | ns    |

| Thermal P             | rotection                               |                                                                                                            |      |      |     |       |

| T <sub>SHDN</sub>     | IC junction thermal shutdown threshold  |                                                                                                            |      | 130  |     | °C    |

| T <sub>HYST</sub>     | IC junction thermal shutdown hysteresis |                                                                                                            |      | 20   |     | °C    |

May 2019 – Revision 04a Page 4 Company Confidential

<sup>7.</sup> All specifications are 100% production tested at  $T_A$  = +25°C, unless otherwise noted. Specifications are over -40°C to +85°C and are guaranteed by design.

Figure 1. Timing Diagram

# **Typical Characteristics**

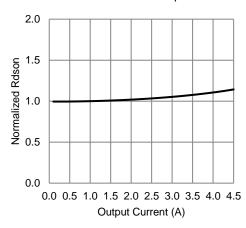

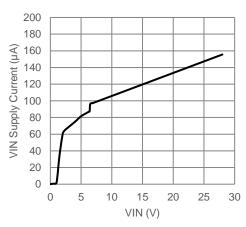

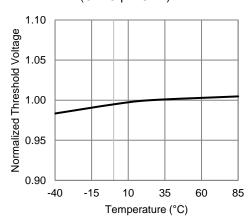

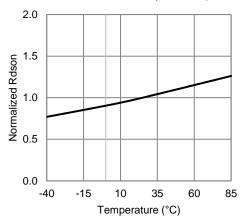

VIN = 5V,  $C_{IN}$  = 0.1 $\mu$ F,  $C_{OUT}$  = 1 $\mu$ F,  $R_{ACOK}$  = 100 $k\Omega$ , OVLO pin = GND, CTRL = GND,  $T_{AMB}$  = 25°C unless otherwise specified.

Normalized Rdson vs. Output Current

Input Supply Current vs. Input Voltage (no load)

Normalized Fixed OVLO vs. Temperature (OVLO pin GND)

Normalized Rdson vs. Temperature ( $I_{OUT} = 1A$ )

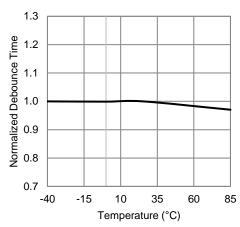

Normalized Debounce Time vs Temperature

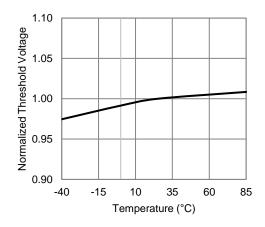

Normalized Adjustable OVLO Threshold vs. Temperature

# **Typical Characteristics**

VIN = 5V,  $C_{\text{IN}}$  = 0.1 $\mu$ F,  $C_{\text{OUT}}$  = 1 $\mu$ F,  $R_{\text{ACOK}}$  = 100 $k\Omega$ , OVLO pin = GND, CTRL = GND,  $T_{\text{AMB}}$  = 25°C unless otherwise specified.

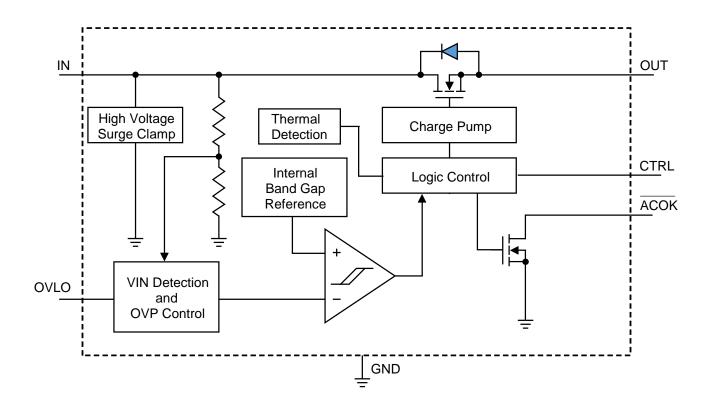

## **Functional Block Diagram**

## **Functional Description**

The KTS1650B is inserted between the power supply or charger source and the load to be protected. The overvoltage protection (OVP) switch features an ultra-low  $36m\Omega$  (typical) on-resistance MOSFET and protects low-voltage systems against voltage faults up to  $+28V_{DC}$ . An internal clamp also protects the device from input surge transients up to 200V. If the input IN pin voltage exceeds the overvoltage threshold, the internal MOSFET is turned off to prevent damage to any downstream components connected to the output. A 15ms debounce time built into the device delays the internal MOSFET turn on time.

The overvoltage protection threshold can be externally programmed with an optional resistor divider to set a threshold between 4V and 24V. With the OVLO input pin tied to GND (or below the external OVLO select voltage), the KTS1650B automatically selects the internal OVLO threshold. The internal overvoltage threshold  $(V_{IN\_OVLO})$  is preset to 6.4V typical.

#### **Device Operation**

During normal operation, with CTRL input low, once IN voltage is present, the main power switch connecting IN and OUT turns on after a 15ms debounce delay (see Functional Diagram). After the debounce delay, a soft-start limits the inrush current for 2ms (typical), during that time OUT voltage ramps up to IN voltage.

The main power switch turns off, OUT disconnected from IN, if one of the following fault condition becomes true. The fault conditions are:

- Overvoltage protection mode (OVP) when either V<sub>IN</sub> > V<sub>IN\_OVLO</sub> or OVLO pin voltage V<sub>OVLO</sub> > V<sub>OVLO\_TH</sub> (if a resistor divider is used to program OVLO).

- Under voltage lockout when VIN below the normal operating range.

- Thermal shutdown.

#### **Internal Main MOSFET Switch**

In normal operating mode (main power switch turned on), the CTRL input must be set to the logic low state (CTRL = GND). The KTS1650B integrates an N-Channel power MOSFET with ultra-low  $36m\Omega$  (typical) onresistance between IN and OUT. The MOSFET is internally driven by an internal charge pump supply rail that generates the gate voltage (VGS) greater than IN.

#### **Overvoltage Lockout (OVLO)**

The KTS1650B has a 6.4V(typical) overvoltage threshold. If the VIN voltage is above this threshold, the internal MOSFET is turned off and OUT is disconnected from IN.

#### **ACOK** Output

The  $\overline{ACOK}$  output is an active-low open-drain flag reporting good operation of the device. A pull-up resistor should be connected from the  $\overline{ACOK}$  pin to the system I/O rail. A fault is flagged when the output is being pulled high in the case of an overvoltage or over-temperature fault occurring.

#### **Thermal-Shutdown Protection**

Both the internal main MOSFET and POK switches are turned off when the junction temperature exceeds +130°C (typ). The device exits thermal shutdown after the junction temperature cools by +20°C (typ).

### Application Information

#### **Input Capacitor**

For most applications, connect a 1nF ceramic capacitor as close as possible to the device from IN to GND. During surge voltage transients, the internal input clamp keeps the input IN pin voltage below 40V, so 50V rated capacitors are ideal for most OVP applications.

#### **OUT Output Capacitor**

The internal soft-start function allows the KTS1650B to charge an output capacitor up to 100µF without turning off due to overcurrent. Cout is recommended to be placed as close as possible to OUT PINs.

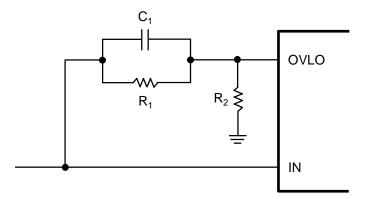

### **External OVLO Adjustment Functionality**

If the OVLO pin is connected to ground, KTS1650B uses the factory programmed OVLO value for its internal OVLO comparator.

If an external resistor-divider is connected to OVLO and  $V_{OVLO}$  exceeds the OVLO select voltage,  $V_{OVLO\_SELECT}$ , the internal OVLO comparator reads the IN fraction fixed by the external resistor divider. Starting with R1 =  $1M\Omega$  to minimize current consumption, R2 can be calculated from the following formula:

$$V_{OVLO\_EXT} = V_{OVLO\_THRESH} \times (1 + \frac{R_1}{R_2})$$

This external resistor-divider is separate from the internal resistor-divider circuit. An external resistor-divider could slow the OVLO response time, affecting the surge protection. An RC divider can be used to improve response speed. The capacitor can be calculated as follows:

$$C_1 > 5 \times t_R \times \left[ \frac{R_1 + R_2}{R_1 R_2} \right]$$

Where  $t_R$  is the rise time of the worst-case transient at IN pin (measured from the start of rising edge to the point where IN reaches  $V_{IN\_OVLO}$ ). See Figure 2.

Figure 2. External OVLO Set Circuit

#### **USB On-The-GO (OTG) Operation**

When used in an OTG application the KTS1650B can provide power from OUT to IN regardless of the condition of the CTRL pin.

When the CTRL pin is LOW (power switch automatically enabled), initially, the OTG voltage applied at OUT will forward bias the power switch bulk diode and present a voltage drop of approximately 0.7V between OUT and

May 2019 – Revision 04a Page 10 Company Confidential

IN. The maximum current in this mode is limited by the thermal performance of the device and at an ambient temperature of 25°C

$$I_{MAX} = \frac{1.28W}{0.7V} = 1.82A$$

This is purely a transitionary condition as once the voltage at IN exceeds 2.1V and the debounce time of 15ms has elapsed, the main power switch will turn fully ON, significantly reducing the voltage drop from OUT to IN.

When the CTRL is HIGH (power switch is OFF), the OTG voltage applied at OUT will also forward bias the power switch bulk diode, but as the switch will not turn ON unless CTRL is pulled LOW, the high forward voltage drop of 0.7V and consequent high power dissipation will remain. For this reason, it is highly recommended to pull CTRL LOW in all OTG applications.

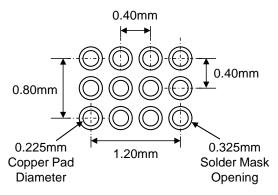

# **Packaging Information**

### WLCSP34-12 (2.156mm x 1.486mm x 0.620mm)

### **Recommended Footprint**

### (NSMD Pad Type)

\* Dimensions are in millimeters.

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.